Performing the Pre-Layout Simulation¶

To perform a pre-layout simulation:

Using Icarus Verilog:

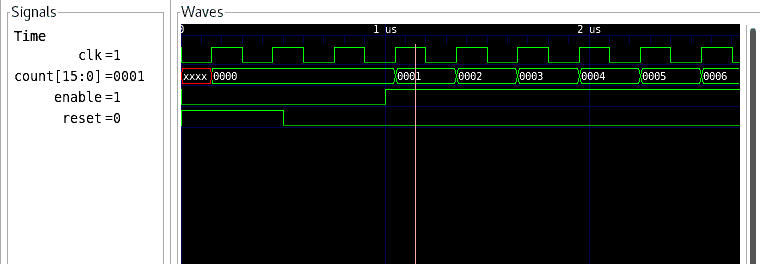

To create the VCD output file that will be used to perform graphical analysis of the

Design, the following lines are added in the TB:initial begin $dumpfile("counter_16bit_tb.vcd"); $dumpvars(0,counter_16bit_tb); $display("\\t\\ttime,\\tclk,\\treset,\\tenable,\\tcount"); $monitor("%d,\\t%b,\\t%b,\\t%b,\\t%d",$time, clk,reset,enable,count); endThe “iverilog” and “vvp” commands are the most important commands available to users of Icarus Verilog. The “iverilog” command is the compiler, and the “vvp” command is the simulation runtime engine.

cd <INSTALL_PATH>/quicklogic-arch-defs/share/symbiflow/tests/counter_16bitThe “iverilog” command supports multi-file designs by two methods. The simplest is to list the files on the command line:

iverilog -o my_design counter_16bit.v counter_16bit_tb.v vvp my_designThis command compiles the design, which is spread across two input files, and generates the compiled result into the “my_design” file.

Another technique is to use a commandfile, which lists the input files in a text file. For example, create a text file called “file_list.txt” with the files listed one per line:#Inside file_list.txt counter_16bit.v counter_16bit_tb.v#Then compile and execute the design with command: iverilog -o my_design -c file_list.txt vvp my_designVCD file is created, it can be viewed using GTKWave: